# 应用笔记

**Application Note**

**AN1142**

APM32F003x4x6 应用注意事项

版本: V1.0

# 1 引言

本应用笔记提供在 APM32F003x4 和 APM32F003x6 应用时需要注意的事项。

# 目录

| 1   | 引言                                 | 1    |

|-----|------------------------------------|------|

| 2   | 硬件应用设计注意                           | 3    |

| 2.1 | MCU 滤波电容设计                         | 3    |

| 2.2 | MCU 供电注意事项                         | 4    |

| 2.3 | 外设模块使用 VDD、 VSS                    | 4    |

| 2.4 | 外部及高频信号                            | 5    |

| 2.5 | Input/Output 信号端口串接限流电阻、 并接电容到 VSS | 5    |

| 2.6 | IO 作为传感器输入端时,接 1MΩ 以上的电阻下拉         | 6    |

| 2.7 | IO 电压不能高于 VDD 电压                   | 6    |

| 2.8 | 暴露在外的端口注意防护                        | 7    |

| 3   | 软件应用注意事项                           | 8    |

| 3.1 | GPIO 操作注意事项                        | 8    |

| 3.2 | ADC 配置注意事项                         | 8    |

| 3.3 | SPI 配置注意事项                         | 8    |

| 3.4 | USART 和 TMR 配置注意事项                 | 8    |

| 3.5 | 低功耗模式操作注意事项                        | 9    |

| 3.6 | I2C注意事项                            | 9    |

| 4   | 仿真器/烧录工具使用注意事项                     | .10  |

| 4.1 | 开发环境支持 IAR、KEIL                    | 10   |

| 4.2 | 编译和烧录                              | 10   |

| 5   | 版本历史                               | . 11 |

# 2 硬件应用设计注意

#### 2.1 MCU 滤波电容设计

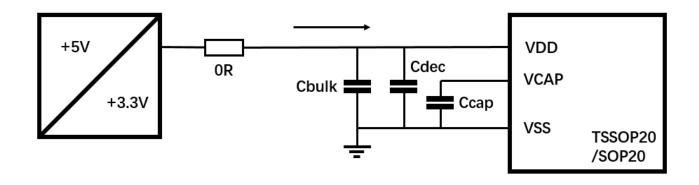

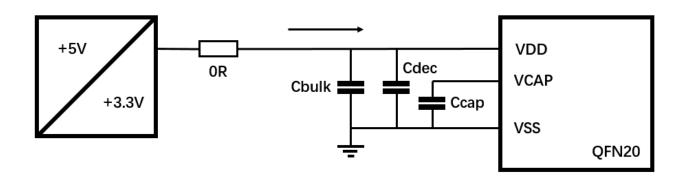

芯片电源端口(VDD、VSS)和 VCAP 引脚需要并接大小滤波电容,如图 1 和图 2 所示。电容的有效性取决于最佳放置和连接类型,PCB 布局需星型走线注意外部电源先经过大小电容再接入芯片,大小滤波电容尽量靠近芯片 4mm 以内放置。参考如下: BULK 电容、CAP 电容、DEC 去耦电容分别为 10uF 以上、2.2uF、100nF。

注意: 低温应用时,电容的实际容值可能会减小,建议在 Vcap 端口接电容(2.2uF),接小电容时可能导致芯片不能正常工作。

图 1 和图 2 中的电阻 0R 可替换为磁珠,在 EMI 测试项(RE)可增加测试裕量,参考参数 600R@100MHz。

图 1 TSSOP20 和 SOP20

图 2 QFN20

#### 2.2 MCU 供电注意事项

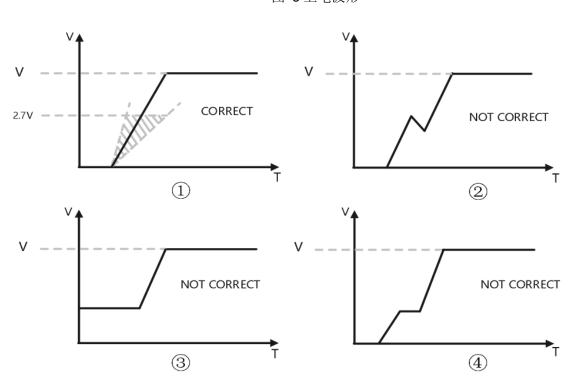

MCU 供电斜坡率需满足数据手册要求的最大值和最小值限值,即大于 0.5V/min 和小于 100V/ms。从 0V 到 5.5V 的时间需要至少需 55us,从 0V 到 2.4V 的时间至少需要 24us,上电速率过快或过慢可能导致 MCU 无法正常工作; MCU 掉电要求掉电至 300mV 以下再重新上电, 以上时间需在全温范围下满足要求。上电启动波形需满足图 3 中①波形, 其余三种波形均不正确。

图 3 上电波形

#### 2.3 外设模块使用 VDD、 VSS

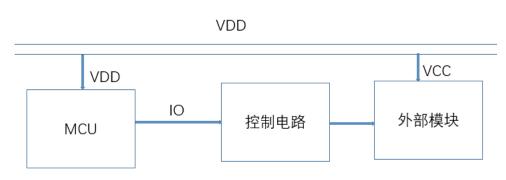

在使用 MCU 控制外部模块的供电或上电过程中,应当避免过快地上电速率,以防止因电流突变而导致的 VDD 电压被拉低的问题。为确保系统稳定运行并保护电路免受潜在损害,建议采用适当的延时措施来平稳地进行供电转换。可以通过增加适当的缓冲元件,例如电容或电阻,来调整上电的速度,不至于 VDD 因为瞬时的大电流需求导致电压骤降,如因此导致 VDD 骤降,下降速度也必须符合 ECU 供电斜坡率要求。(如图 4 和图 5 使用示例)

图 4 IO 控制外设模块

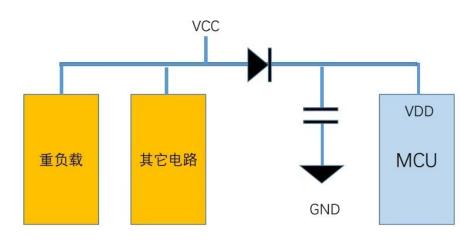

为了规避电源波动,在 MCU 供电 3.6V 以上的应用中,在电路上串一个低压降二极管或串一个 10R 电阻和并一个 10uF 以上电容,组成抗快速掉电电路。如果电容足够大,掉电将很缓,且降电幅度可以很小。

注:如锗二极管导通时会有 0.2V 压降,这会让 MCU 的供电比原来降低 0.2V,如使用 ADC 可能精度受影响。

图 5 外设共用电源

### 2.4 外部及高频信号

- 如过零信号、继电器信号、AC 负载等,需注意是否会产生瞬间加大负载的情况,可通过旁路电容方式减缓负载冲击。

- 如高频 IIC 时钟线、高频 SPI 时钟线等,需注意是否会产生瞬间尖峰电流。

- 控制 LDO 将后级电源接入电路时,在 LDO 后端电路中加 300uF 大电容或延时电路,防止 LDO 接入时导致电源电压骤降,引起 MCU 复位。

# 2.5 Input/Output 信号端口串接限流电阻、 并接电容到 VSS

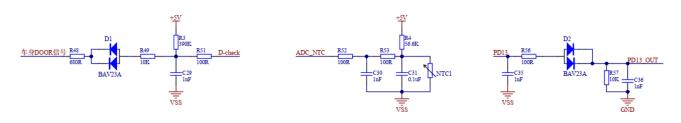

Input/Output 端口(比如: ADC, 外部中断, 通信接口等), 建议电路设计时串接保护电

阻,阻值需考虑并计算理论最大电流不能超出芯片端口承受的极限参数; 串接的电阻和并接电容均要尽可能地靠近芯片引脚放置, 且须先串接电阻, 再并接电容。 外设模块的滤波电容的地一定要接(VDD、 VSS)经过大小滤波电容后的地。如图 6, IO 端口串接 100R 电阻,并接 1nF电容。

注意: PCB 相互连接的设计中(类似灯具和控制模块分开、 传感器和控制模块分开), 这种串接电阻, 并接电容 一定要放置在芯片的 PCB 板上, 合理的参数及放置位置能有效防止 ESD/EOS 对芯片端口的损坏。

图 6 电阻电容连接示例

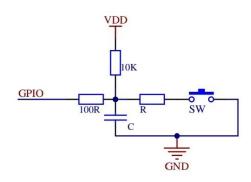

如果是按键电路,推荐如下:

图 7 按键电路

图 7 的 C 推荐用 220nF 电容,在按键旁串一个小电阻 R,如 1k或 100R,同时在画板时尽量将电容 C 靠近按键 SW 放置。规避按键产生的冲击负压。

#### 2.6 IO 作为传感器输入端时,接 1MΩ 以上的电阻下拉

同一个 PORT 的不同引脚只能配置同一个外部触发中断,IO 口读脉冲时,容易干扰别的 IO 口产生中断计数,在传感器输入端口接  $1M\Omega$  以上的电阻下拉,让 IO 口电平稳定在固定电平,避免中断误触发或重复计数。

#### 2.7 **IO** 电压不能高于 **VDD** 电压

当 IC 未有 VDD 供电,而 IO 口却存在电压时,则该电压会通过上拉保护二极管向 IC 进行供电。或是当 IC 有 VDD 供电,但 IO 口却存在比 VDD 更高电压时, 该电压与 VDD 之间的压差使得上拉保护二极管导通,使得电流流入 VDD。正常情况下 IO 不能高于超过 VDD 0.3V。

此现象易引发以下危害:

- (1) 电流太大会将使 IO 口上的钳位二极管迅速过载并使其损坏。

- (2) 会使单片机复位不成功。

- (3) 会使芯片程序紊乱。

- (4) 会出现闩锁效应。

### 2.8 暴露在外的端口注意防护

- 如通信口,需要加 ESD 防护措施。可在信号线上串联一个小电阻 100R 限制 ESD 电流的幅度;可使用瞬态电压抑制器二极管(TVS)并联在信号线上,靠近接口位置。

- 烧录口存在热拔插风险,需注意防护,连接时先接触 GND 再接触 IO。

- 复位引脚应当外接电容但是不应过大,可能会导致引脚不能完全拉低引起烧录异常,建议电容接 100nF。

## 3 软件应用注意事项

#### 3.1 **GPIO** 操作注意事项

- 1. 未使用到的 GPIO 端口,需将其设置为输出低电平或外部接 100  $\Omega$  电阻下拉。

- 2. GPIO 端口的复用功能, 需避免不同 GPIO 引脚配置相同的复用功能!

- 3. 芯片 VDD 上电从 0V-2.4V 区间, GPIO 端口处于不确定态,需注意 GPIO 不定态对后级驱动电路稳定性的影响; VDD 上电高于 2.4V, 芯片完成上电复位后, GPIO 端口状态按照程序的设置执行。

- 4.PA1 进入休眠模式时,若保持输入状态则状态将为拉低,如果有在休眠时保持 PA1 拉高的应用,应该在进入休眠模式前将 PA1 端口配置为输出。

5.应避免 GPIO 的主函数配置和中断配置发生冲突。可以使用变量作为互斥标志作为规避或在中断函数中只做标记,GPIO 的赋值放在 main 中 while 任务中执行。

例如:在主程序的 while 中不断配置 PD3,启用定时中断,在中断中对 PD3 进行翻转,运行后会出现 PD3 翻转异常的情况。

#### 3.2 ADC 配置注意事项

在单通道连续转换模式下,在 ADC1\_ConversionConfig 库函数中,配置 CSR 之前,首先配置 位连续扫描模式,否则在初始化第二个通道时会导致 EOC 不能置位,进而不能使用 ADC。

具体操作步骤为:

- (1) 配置连续扫描模式;

- (2) 配置 CSR;

- (3) 正常配置连续或非连续模式;

- (4) 使能扫描模式。

## 3.3 SPI 配置注意事项

在 SPI 的应用中,当主机在通信时重启,从机由于缓存数据没有发送完成,TXBEF 为空,但是发送缓存仍有其他数据,此时再进行通信会导致通信故障。

修改 SPI 工作参数时,需要复位 SPI 时钟并重新配置一遍。如果直接初始化参数,会导致无法通信成功。

## 3.4 USART 和 TMR 配置注意事项

1.使用 PB4、PB5 作为串口输入输出引脚时,由于这两个引脚只有开漏输出,需要接上拉电阻配合使用。

2.应避免以下两种应用场景:

若打开 USART2,则 TMR1A\_CH1(PD1)无法输出 PWM; 若打开 USART3,则 TMR2 CH3(PA3)无法输出 PWM。

#### 3.5 低功耗模式操作注意事项

在需要重复唤醒的应用中,应当避免在中断服务函数中进入低功耗模式,可能导致芯片不能重复唤醒。

#### 3.6 **I2C** 注意事项

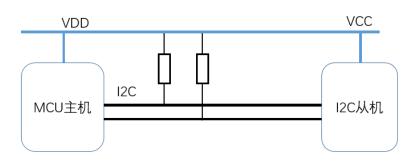

SCL/SDA 在上拉电源突然掉电再回升的过程中,SCL/SDA 电压和逻辑时序的组合会存在触发 START 而无法触发 STOP 的可能,导致总线一直处于 BUSY 状态。建议规避方案:

- 1. I2C 的上拉电源须保证稳定,预防使用过程中电源不稳掉落过低的情况。常见 I2C 主从通信的场景,建议硬件如下设计:

- a. 主机和从机共用电源;

图 8 I2C 通信电路

- b. 主机和从机不能共用电源时,建议上拉电阻电源连主机 MCU 电源。

- 2. 通过复位从机也可实现释放总线。如果是 EEPROM 作为从机时,无法使用软件复位从机的方法,需要在 I2C 主机在建立新的通信时,增加总线释放功能。由于总线锁死是概率性的,可以增加总线 BUSY 状态超时功能。二者结合可以提高系统的鲁棒性。

- 3. 总线上的 I2C 设备,如果能识别断电,在断电前把 I2C 模块关闭。

# 4 仿真器/烧录工具使用注意事项

#### 4.1 开发环境支持 IAR、KEIL

- 1. IAR 建议使用 V8.50.5 版本及以上。

- 2. KEIL 建议使用 MDK-ARM V5.36 版本。

注意:使用低版本的 MDK 编译不通过的工程,更新到高版本后,原报错的工程不能用,需重新解压 SDK 程序使用。

3. J-Link 软件建议使用 V7.96o 版本及以上。

#### 4.2 编译和烧录

1.应使用极海官网上发布的 APM32 PROG V1.014 烧录器上位机协助配合 OB。

F003 通过 JLink 或 ST-LINK 进行调试烧录时,容易进入自锁状态。

通常情况下,用户都会在 main 函数中自行操作 OB,而操作 OB 被中断或出现不完整操作,芯片就容易被锁住,因为 OB 地址上还有关于读保护和写保护的配置位。除此之外,OB 值的非正常变化,也有可能导致程序运行异常或系统崩溃。

- 2. ST-LINK 仅支持 3.3V 电源域的 SWD 通信, 5V 供电时会出现无法连接和识别芯片的情况,烧录和调试时建议使用 3.3V 外部供电转为 ST-LINK 直供或将 SWD 引脚接外部上拉。

- 3. 当烧录软件不提供 APM32F003 的料号时,可以选择 M0 或 M0+内核的料号进行烧录或使用 J-FLASH。

# 5 版本历史

表格 1 文件版本历史

| 日期     | 版本  | 变更历史 |

|--------|-----|------|

| 2025.1 | 1.0 | 新建   |

# 声明

本手册由珠海极海半导体有限公司(以下简称"极海")制订并发布,所列内容均受商标、著作权、软件著作权相关法律法规保护,极海保留随时更正、修改本手册的权利。使用极海产品前请仔细阅读本手册,一旦使用产品则表明您(以下称"用户")已知悉并接受本手册的所有内容。用户必须按照相关法律法规和本手册的要求使用极海产品。

#### 1、权利所有

本手册仅应当被用于与极海所提供的对应型号的芯片产品、软件产品搭配使用,未经极海许可,任何单位或个人均不得以任何理由或方式对本手册的全部或部分内容进行复制、抄录、修改、编辑或传播。

本手册中所列带有"®"或"TM"的"极海"或"Geehy"字样或图形均为极海的商标,其他在极海产品上显示的产品或服务名称均为其各自所有者的财产。

#### 2、无知识产权许可

极海拥有本手册所涉及的全部权利、所有权及知识产权。

极海不应因销售、分发极海产品及本手册而被视为将任何知识产权的许可或权利明示或默示地授予用户。

如果本手册中涉及任何第三方的产品、服务或知识产权,不应被视为极海授权用户使用前述第三方产品、服务或知识产权,也不应被视为极海对第三方产品、服务或知识产权提供任何形式的保证,包括但不限于任何第三方知识产权的非侵权保证,除非极海在销售订单或销售合同中另有约定。

#### 3、版本更新

用户在下单购买极海产品时可获取相应产品的最新版的手册。

如果本手册中所述的内容与极海产品不一致的,应以极海销售订单或销售合同中的约定为准。

#### 4、信息可靠性

本手册相关数据经极海实验室或合作的第三方测试机构批量测试获得,但本手册相关数据难 免会出现校正笔误或因测试环境差异所导致的误差,因此用户应当理解,极海对本手册中可能出 现的该等错误无需承担任何责任。本手册相关数据仅用于指导用户作为性能参数参照,不构成极 海对任何产品性能方面的保证。

用户应根据自身需求选择合适的极海产品,并对极海产品的应用适用性进行有效验证和测试,以确认极海产品满足用户自身的需求、相应标准、安全或其它可靠性要求;若因用户未充分对极海产品进行有效验证和测试而致使用户损失的,极海不承担任何责任。

#### 5、合规要求

用户在使用本手册及所搭配的极海产品时,应遵守当地所适用的所有法律法规。用户应了解产品可能受到产品供应商、极海、极海经销商及用户所在地等各国有关出口、再出口或其它法律的限制,用户(代表其本身、子公司及关联企业)应同意并保证遵守所有关于取得极海产品及/或技术与直接产品的出口和再出口适用法律与法规。

#### 6、免责声明

本手册由极海"按原样"(as is)提供,在适用法律所允许的范围内,极海不提供任何形式的明示或暗示担保,包括但不限于对产品适销性和特定用途适用性的担保。

极海产品并非设计、授权或担保适合用于军事、生命保障系统、污染控制或有害物质管理系统中的关键部件,亦非设计、授权或担保适合用于在产品失效或故障时可导致人员受伤、死亡、财产或环境损害的应用。

如果产品未标明"汽车级",则表示不适用于汽车应用。如果用户对产品的应用超出极海提供的规格、应用领域、规范,极海不承担任何责任。

用户应该确保对产品的应用符合相应标准以及功能安全、信息安全、环境标准等要求。用户 对极海产品的选择和使用负全部的责任。对于用户后续在针对极海产品进行设计、使用的过程中 所引起的任何纠纷,极海概不承担责任。

#### 7、责任限制

在任何情况下,除非适用法律要求或书面同意,否则极海和/或以"按原样"形式提供本手册 及产品的任何第三方均不承担损害赔偿责任,包括任何一般、特殊因使用或无法使用本手册及产 品而产生的直接、间接或附带损害(包括但不限于数据丢失或数据不准确,或用户或第三方遭受 的损失),这涵盖了可能导致的人身安全、财产或环境损害等情况,对于这些损害极海概不承担 责任。

#### 8、适用范围

本手册的信息用以取代本手册所有早期版本所提供的信息。

©2025 珠海极海半导体有限公司 - 保留所有权利